Vivado 和 matlab 联合生成算法模块代码

FPGA的一大应用就是数字信号处理(DSP),尤其是大数据量高速处理的场合,比如雷达,成像,超声等领域。

但是直接用Verilog实现DSP算法,是一件很费时费力的事情,而且改动也不是很方便。目前有几种折中的办法,

一是用HLS,大概的思路就是用C/C++先编写算法,然后转译为Verilog语言;另一种就是用MATLAB等工具,

直接生成Verilog代码。

步骤如下:

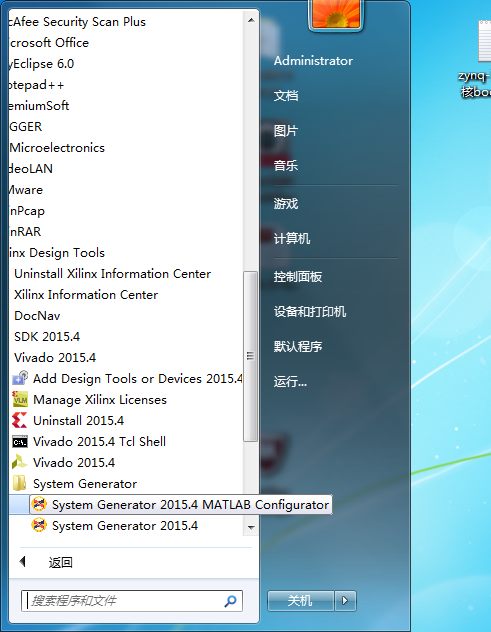

首先,关联MATLAB和Vivado

在【开始】菜单,找到配置工具,打开

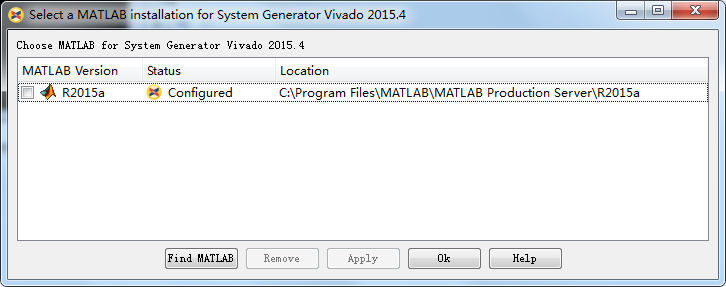

选择MATLAB路径

注意到 R2015a 目录 即可。

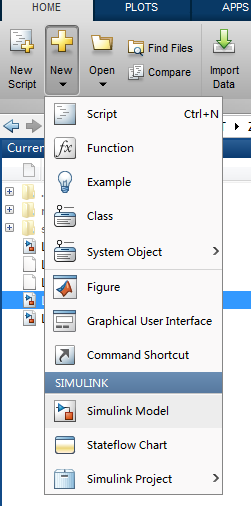

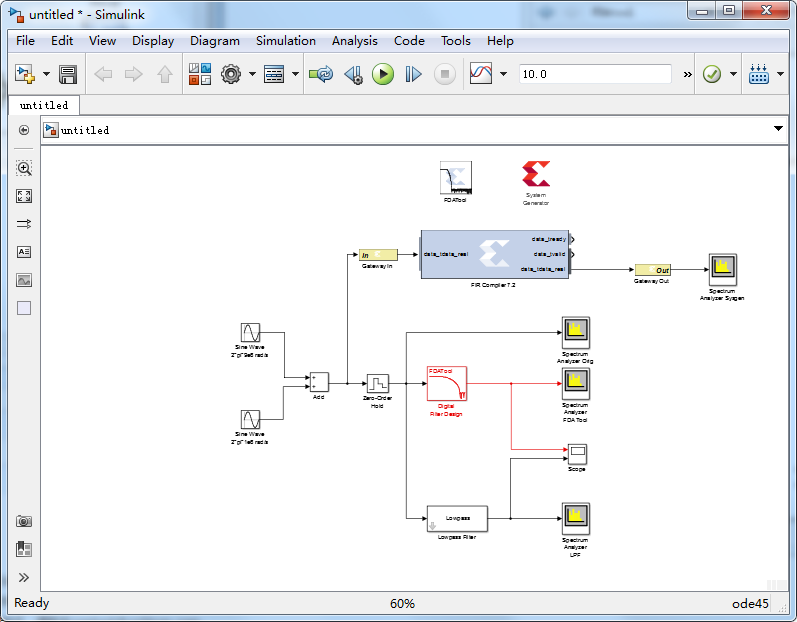

打开MATLAB2015,新建一个simulink模型

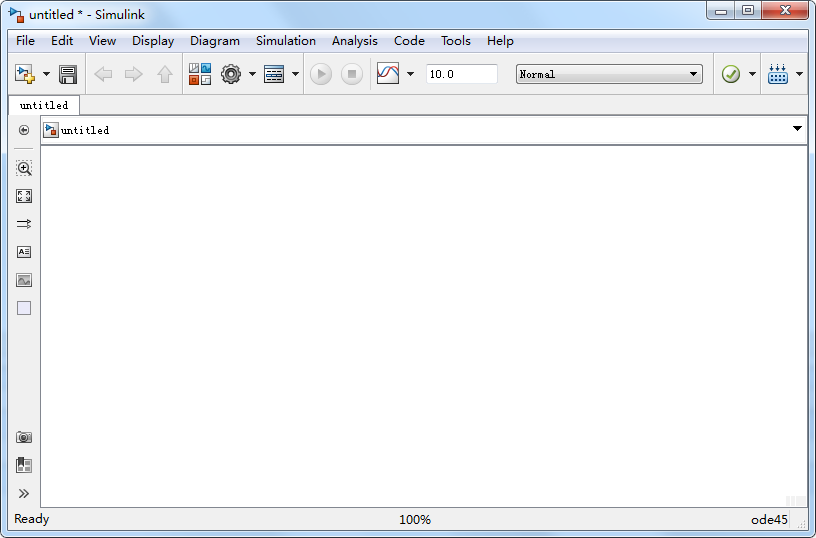

可以看到如下一个空白窗体

打开【simulink Library】

找到Xilinx相关仿真模块

拖到simulink 模型窗体即可,完毕后联线

单击【RUN】进行仿真即可

最后,生成Vivado项目工程,双击 【System Generator】

【System Generator】

选择正确的芯片型号和你自己使用的语言,目录选择默认即可。

单击【Generate】,生成工程。

完成后,可以在【netlist】文件夹的【ip_catalog】子目录中找到xpr工程文件

双击可以用Vivado打开,编译综合后即可生成IP核。

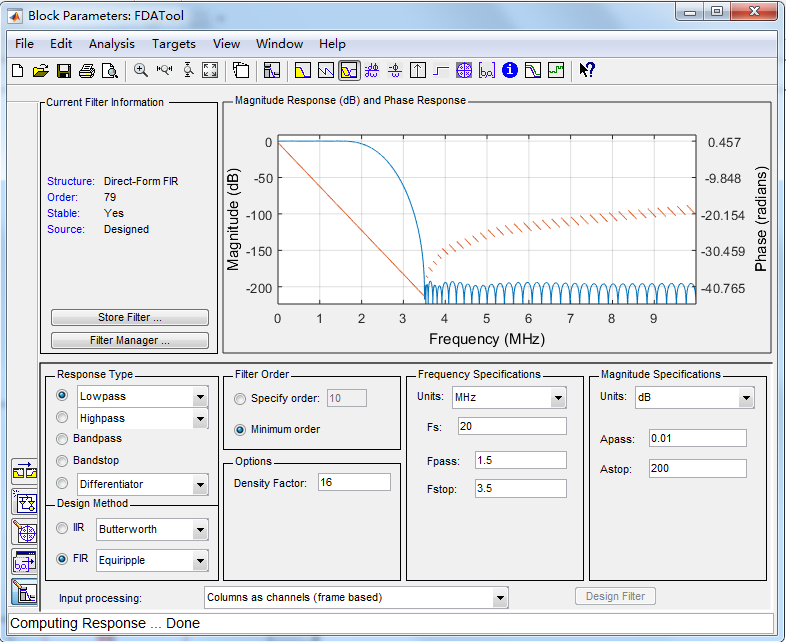

滤波器参数如下

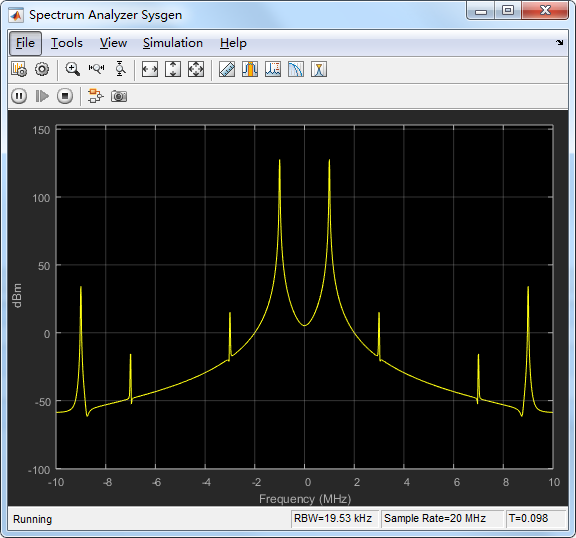

原始信号频谱

模块仿真输出信号频谱-8it定点,可以看到明显的量化噪声

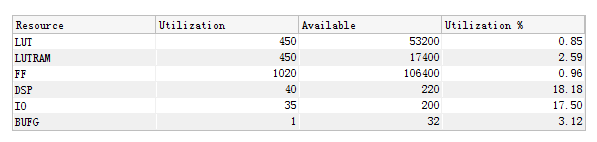

最后消耗资源如下

详细的FDATool及相关组件的使用方法,请查阅MATLAB help和Xilinx的相关手册。

参考资料:

1.Xilinx UG948 《Vivado Design Suite Tutorial,Model-Based DSP Design Using System Generator》

2.Xilinx UG958 《Vivado Design Suite Reference Guide,Model-Based DSP Design Using System Generator》