DRAM 内存介绍(二)

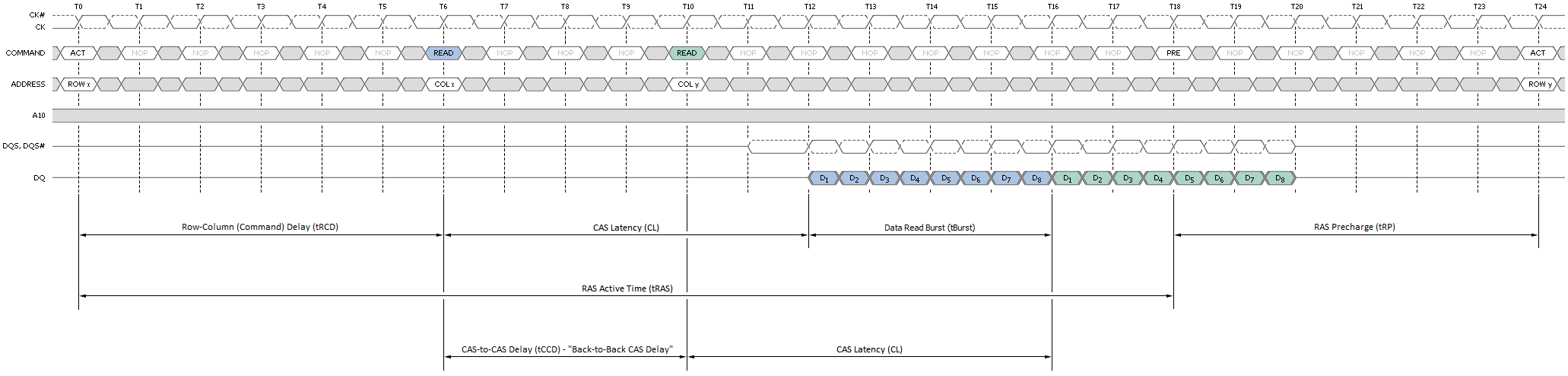

DDR3 SDRAM的读写操作都是burst相关的,在一个address启动读写操作后,它都要连续进行burst length的byte读写,就像前一章的图中,ACT命令后,会跟着一个多个读写命令。read burst 的长度总是4 clocks,这是因为DDR传输数据频率是主机的两倍,4 clocks x 2 transactions/clock = 8 transactions or 8 bits per bank。

DDR3的内存地址中,可以包括以下的位:1位chip select位,0表示rank0,1表示rank1;bank选择位 BA0-BA2 ,DDR3是8个bank,所以3位就足够了,GDDR5是16个bank,所以需要4位,HBM也是16个bank,也需要4位。page选择位A0-A13,表示每个bank内,有16,384 (214) pages。列用A00-A09 表示,每个page有210 = 1,024列。A12bit通常作为Burst Chop bit,如果A12 是high,则在一个读burst中,仅有一半的数据被发送。A10 bit用来决定precharge是对于一个bank(A10 low)还是对于所有bank(A10 high)。

图一, 内存读写操作

数据输入/输出 pins DQ0-DQ63 在cpu和DIMM之间提供了64bit宽的数据接口,比如Intel Core i7处理器,有三个64bit宽的memory channel,所以内存总线宽度为192bit, intel i5处理器则有两个64bit的memory channel,所以内存总线宽度是128bit。

每个channel能够管理操作两个DIMM,这意思是说每个channel最多有4个rank,在同一个channel中增加DIMM,并不能增加内存总线宽度,但这增加了bank的数目,提高了同时操作page的能力。

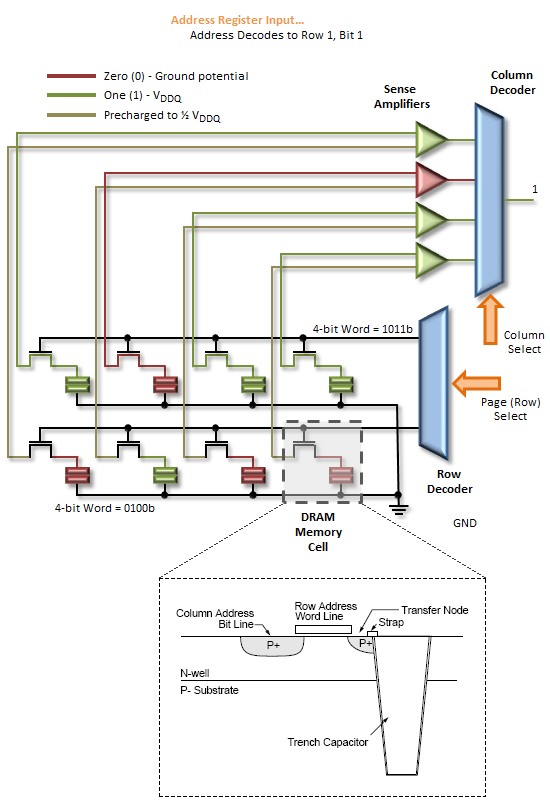

图二,内存读写操作

在图二的例子中,我们假定bank中没有打开的page,也就是说bank处于precharge状态,我们可以启动访问一个新的page。第一步,选择page,第二步,选择列,第三步,burst数据到内存总线。在图中,行地址是1位,列地址是4位,所存的数据总共是2 x 4-bit x 1 (bank)。

一个ACT命令指定访问行地址解码器,这将触发输入传感放大器中的row address word line,就像前一篇文章介绍的,这需要消耗tRCD cycles的最小等待时间,才能发送下一条命令。如果设置时序过小,可能会导致数据出错。接着,读命令伴随着列地址访问,选择了coloumn address bit line,这将需要消耗CL cycles,然后传感放大器的word line被激活,传感放大器开始工作,开始读burst操作,之后就是precharge操作,需要消耗tRP的cycles时间。

Click to enlarge

图三. bank读操作时序图

图三显示了16byte的读写时序图。